# Implementation of Fuzzy Based Grid-Tied PV System for Single Phase Transformer less Inverter with **Charge Pump Circuit Concept**

Anil Tekale<sup>1</sup>, Radharaman Saha<sup>2</sup>, Pratik Ghutke<sup>3</sup>, Swapna God<sup>4</sup>

<sup>1</sup>M. Tech Scholar, Integrated Power System, <sup>2</sup>Head of Department, <sup>3,4</sup>Assistant Professor 1, 2, 3 Department of Electrical Engineering, TGPCET, Nagpur. India <sup>4</sup>Department of Electrical Engineering, HSBPVTs GOI, College of Engineering, India

**ABSTRACT**

How to cite this paper: Anil Tekale | Radharaman Saha | Pratik Ghutke | Swapna God "Implementation of Fuzzy Based Grid-Tied PV System for Single Phase Transformer less Inverter with Charge Pump Circuit Concept" Published in International Journal of Trend in Scientific Research and

Development (ijtsrd), ISSN: 2456-6470, Volume-3 | Issue-4, June 2019, pp.163-171, URL: https://www.ijtsrd.c om/papers/ijtsrd23 583.pdf

IITSRD23583

Copyright © 2019 by author(s) and International Journal of Trend in Scientific Research and Development Journal. This is an Open Access article

distributed under the terms of the **Creative Commons**

clamped (NPC), active NPC, and half-bridge inverters); flexible grounding configuration; capability of reactive power flow; and high efficiency. By using

### Development

practical application in grid-tied PV systems.

Keywords: Grid-tied inverter, Charge Pump Circuit, Transformer Less Inverter, Leakage Current Elimination, Fuzzy Logic Control.

This paper proposes a implementation of a single phase transformer less

photovoltaic inverter for grid connect PV system. We are developing new

topology to eliminate the leakage current in which concept of charge pump

circuit is introduced. In this paper, for controlling purpose we are utilizing Fuzzy

Logic Controller. The neutral of the grid is directly connected to the negative

polarity of the PV panel that creates a constant common mode voltage and zero

leakage current. During the negative cycle, the charge pump circuit generates the

negative output voltage of the proposed inverter. Therefore, according to the

proportional resonant control strategy is used to control the injected current.

There are various advantages of the proposed inverter they are the neutral of the

grid is directly connected to the negative terminal of the PV panel, so the leakage

current is eliminated, its compact size; low cost; the used dc voltage of the

proposed inverter is the same as the full-bridge inverter (unlike neutral point

simulation result we can verify the concept of the proposed inverter and its

### 1. INTRODUCTION

Over the last two decades, the photovoltaic (PV) power systems have become very popular among the renewable energy sources, because they generate electricity with no moving parts, operate quietly with no emissions, and require little maintenance. [1], [2]. Distributed grid-connected PVs are playing an increasingly role as an integral part of the electrical grid. However, due to the large stray capacitors between the PV panels and the ground, PV systems suffer from a high common mode (CM) current, which reduces the system efficiency and may cause safety issues like electric shock. In order to eliminate the leakage currents, transformers are commonly used in the PV system to provide galvanic isolation. However, it possesses undesirable properties including large size, high cost, and weight with additional losses. Thus, eliminating the transformer is a great benefit to further improve the overall system efficiency, reduce the size, and weight.

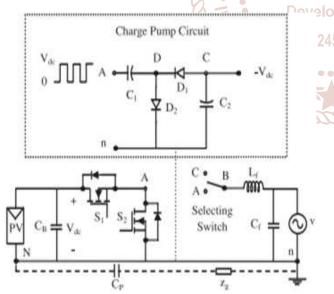

This project introduces a new transformer less inverter based on charge pump circuit concept, which eliminates the leakage current of the grid-connected PV systems using a

unipolar sinusoidal pulse width modulation (SPWM) technique. In this solution, the neutral of the grid is directly connected to the negative terminal of the charge pump circuit, so the voltage across the parasitic capacitor is connected to zero and the leakage current will be eliminating. The charge pump circuit is implemented to generate negative output voltage. There is not any limitation on the modulation strategy of the proposed inverter because the leakage current is eliminated by the circuit topology. The proposed topology consists of only four power switches, so the cost of the semiconductors is reduced and the power quality is improved by three-level output voltage in order to reduce the output current ripple. During operation of the proposed inverter, the current flows through two switches; thus, the conduction loss is also lower. The used dc voltage of the proposed inverter is the same as the FB inverter (unlike NPC, ANPC, and half-bridge (HB) inverters) [3]. And many other topologies such as H5, H6, and highly efficient and reliable inverter concept (HERIC) were proposed to reduce the leakage current with disconnecting of the grid from the PV during the freewheeling modes [4]. The proposed inverter is capable of delivering reactive power into grid too.

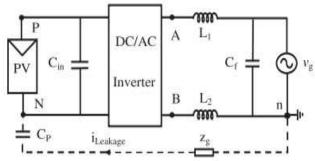

Fig. 1 illustrates a single-phase grid-tied transformer less inverter with CM current path, where P and N are the positive and negative terminals of the PV, respectively. The leakage current (iLeakage) flows through a parasitic capacitor (CP) between the filters (L1 and L2), the inverter, grid, and ground impedance (zg). This leakage current may cause safety problems, reduce the quality of injection current to the grid, as well as decrease the system efficiency [5].

Fig. 1. Block diagram of a single-phase grid-connected transformer less inverter with a leakage current path.

In order to eliminate the leakage current, the CM voltage (CMV) (v<sub>cm</sub>) must be kept constant during all operation modes according to [6]. The vcm with two filter inductors

$$V_{cm} = \frac{V_{An} + V_{Bn}}{2} + \frac{(V_{An} - V_{Bn})(L_1 - L_2)}{2(L_1 + L_2)}$$

Internation of Trend in

V<sub>An</sub> and V<sub>Bn</sub> are the voltage differences between the midpoints A and B of the inverter to the dc bus minus terminal N, respectively. If  $L_1 = L_2$  (asymmetrical inductor), v<sub>cm</sub> is calculated according to (1) and the leakage current appears due to a varying CMV. If  $L_1 = L_2$  (symmetrical inductor), v<sub>cm</sub> is simplified to

$$V_{cm} = \frac{V_{An} + V_{Bn}}{2} = Constant$$

(2)

In this state, the CMV is constant and the leakage current is eliminated. In some structures such as the virtual dc-bus inverter [7] and NPC inverter, one of the filter inductors is zero and only one filter inductor is used. In this state, after simplification of vcm, it will have a constant value according to (3) and the leakage current will be eliminated

$$V_{cm} = \frac{V_{An} + V_{Bn}}{2} + \frac{(V_{An} - V_{Bn})}{2} = Constant(L_1 = 0)$$

$$V_{cm} = \frac{V_{An} + V_{Bn}}{2} - \frac{\left(V_{An} - V_{Bn}\right)}{2} = Constant\left(L_1 = 0\right) \tag{3}$$

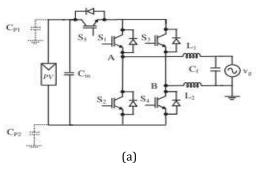

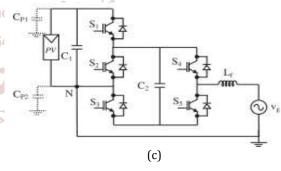

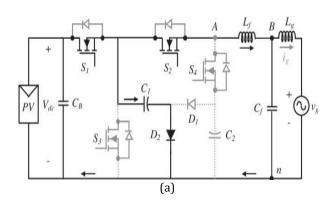

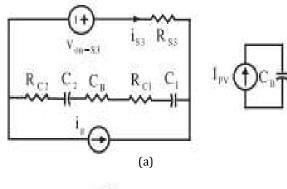

As shown in Fig. 2, there are various transformer less grid connected inverters based on the FB inverter in the literature to overcome these problems. The H5 inverter that is a FB-based inverter topology, compared to the conventional FB inverter, needs one additional switch (S5) on the dc side to decouple the dc side from the grid as shown in Fig. 2(a).

As shown in Fig. 2(b), the HERIC topology needs two extra switches on the ac side to decouple the ac side from the PV module in the zero stage. HERIC combines the merits of unipolar and bipolar modulation.

Another solution to eliminate the leakage current is the direct connection of the negative PV terminal to the neutral point of the grid, such as the virtual dc-bus inverter and the unusual topology, as shown in Fig. 2(c), the virtual dc-bus inverter is composed of five insulated-gate bipolar transistors (IGBTs), two capacitors, and one filter inductor

The virtual dc-bus generates the negative output voltage. The main drawback of this topology is that there is no path to charge the capacitor C<sub>2</sub> during the negative cycle and this will cause a high output total harmonic distortion (THD). The topology presented, which is shown in Fig. 2(d), has a common ground with the grid.

Fig.2. Single-phase grid-tied transformer less PV inverter topologies: (a) H5 inverter, (b) HERIC inverter, (c) virtual dc-bus inverter and (d) CM inverter proposed

The number of semiconductors used in this topology is low. However, the output voltage of this inverter is only two levels including positive and negative voltages without creating the zero voltage, which requires a large output inductor L2 and a filter. The inductor medium-type inverter also called "Karschny" is another topology that is derived from the buck-boost topology.

This paper introduces a new transformer less inverter based on charge pump circuit concept, which eliminates the leakage current of the grid-connected PV systems using a unipolar sinusoidal pulse width modulation (SPWM) technique. The proposed topology consists of only four power switches, so the cost of the semiconductors is reduced and the power quality is improved by three-level output voltage in order to reduce the output current ripple.

### 2. Proposed Topology and Modulation Strategy 2.1. Charge Pump Circuit Concept

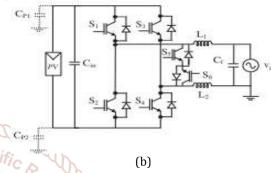

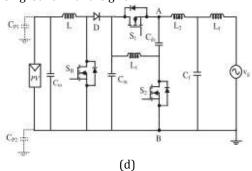

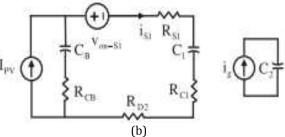

The concept of a simple charge pump circuit to be used in the proposed topology to generate the inverter negative output voltage is shown in Fig. 3. The circuit consists of two diodes  $(D_1, D_2)$  and two capacitors  $(C_1, C_2)$ . The capacitor  $C_1$  is used to couple the voltage point of A to the node D. Two Schottky diodes  $D_1$  and  $D_2$  are used to pump the output voltage.

In steady state, the output voltage of the negative charge pump circuit (v<sub>Cn</sub>) can be derived by

$$V_{cm} = -V_{dc} + V_{cut - in - D_1} + V_{cut - in - D_2}$$

(4)

### Where,

$V_{dc}$  is the input voltage,  $V_{cut-in-D1}$  and  $V_{cut-in-D2}$  are the cut-in voltages of the diodes D<sub>1</sub> and D<sub>2</sub>, respectively. For high power applications, these values can be negligible.

Fig.3. Schematic diagram of the proposed inverter including the charge pump circuit.

The above principle is integrated into the proposed inverter by using additional switching devices. In summary, the charge pump circuit in the transformer less inverter has the following characteristics for grid-tied applications.

- 1. This circuit has a common line with the negative terminal of the input dc voltage and the neutral point of the grid that causes the leakage current to be eliminated.

- The charge pump circuit has no active device and it has a lower cost for grid-tied applications.

### 2.2. Proposed Methodology

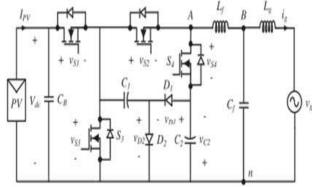

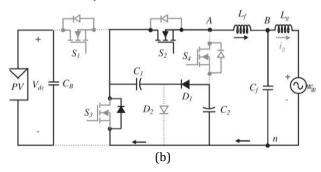

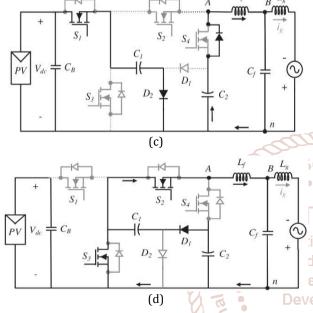

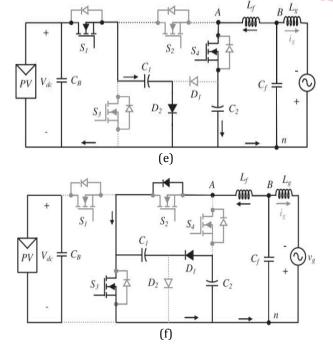

As shown in Fig. 4, the proposed topology consists of four power switches  $(S_1 - S_4)$ , two diodes  $(D_1, D_2)$ , two capacitors (C<sub>1</sub>, C<sub>2</sub>) based on the charge pump circuit as described in Section 2.1.

Fig.4. Proposed single-phase transformer less gridconnected inverter

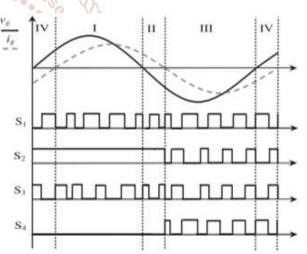

This new topology is modulated using simple SPWM. Fig. 5 shows the gate drive signals for the proposed inverter under the current lagging condition. According to the direction of the inverter output voltage and output current, the operation of the proposed inverter is divided in four regions as shown in Fig. 6.

Fig.5. Switching pattern of the proposed topology with reactive power flow

Region I: The inverter output voltage and the output current are positive; energy is transferred from dc side to grid side as shown in Fig. 6(a).

Region II: The inverter output voltage is negative and the output current is positive; energy is transferred from grid side to dc link as shown in Fig. 6(c).

Region III: the inverter output voltage and the output current are negative; energy is transferred from dc link to grid side as shown in Fig. 6(e).

Region IV: the inverter output voltage is positive and the output current is negative; energy is transferred from grid side to dc side as shown in Fig. 6(g)

When the switches  $S_1$  and  $S_2$  are ON, the output voltage of the inverter  $(v_{An})$  will be  $+V_{dc}$  (positive state) as shown in Fig. 6(a) and (g). During this time interval, diode  $D_1$  is reverse biased and D<sub>2</sub> is ON, so the capacitor C<sub>1</sub> is charged through diode D<sub>2</sub> and the voltage across the capacitor C<sub>2</sub> maintains to be constant. In this state, when the switches S<sub>2</sub> and S<sub>3</sub> are ON, v<sub>An</sub> will be 0 (zero state) as shown in Fig. 6(b) and (h).

Fig: 6 Operational stages of the proposed inverter during (a), (b) region I, (c), (d) region II, (e), (f) Region III and (g), (h) region IV

Develop (a) vAn = +Vdc, ig > 0. (b) vAn = 0, ig > 0. (c) vAn = -Vdc, ig > 0. (d) vAn=0, ig>0. (e) vAn=-Vdc, ig<0. (f) vAn=0, ig<0. (g) vAn = +Vdc, ig < 0. (h) vAn = 0, ig < 0.

> In the regions II and III, the negative and zero voltage levels are produced. Fig. 6 (c) and (e) shows the equivalent circuit that S4 and S1 are ON. The negative voltage is generated, when switch S4 is turned ON and the voltage across the capacitor C<sub>2</sub> appears at the inverter output voltage (v<sub>An</sub> = -V<sub>dc</sub>) (negative state).

> The voltage across the capacitor C<sub>1</sub> can be kept constant in this state by the modulation strategy. In this period, the circuit operation of the zero state is similar to the zero state of positive half-period of the grid as shown in Fig. 6 (b) and (h). In this case, the charging time constant of capacitor C2  $(\tau C_2)$  can be expressed as follows:

$$\tau_{C2} = \operatorname{Re} {}_{1}C_{e1} \tag{5}$$

The current through capacitors (i<sub>capacitors</sub>) is calculated by

$$i_{Capacitors} = C_{e1} \frac{V_{C1} - V_{C2}}{\tau_{C2}}$$

(6)

According to (5), the charging time constant of  $C_2$  is larger than its natural discharging time constant and  $V_{\text{C1}}\text{--}\,V_{\text{C2}}$  has a very small value in steady state.

### 3. Analysis of the Proposed Topology

### 3.1. Current Stress Analysis and Capacitor Design

In this section, current stress analysis of the proposed topology has been presented. As capacitor C<sub>1</sub> is charged

Page: 166

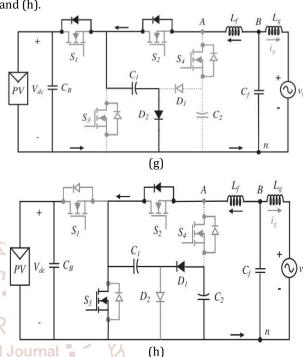

through switch S<sub>1</sub> and capacitor C<sub>2</sub> is charged through switch  $S_3$ , the maximum value of the current stress occurs on the switches  $S_1$  &  $S_3$ . Simulation results of the current in the switches S<sub>1</sub> & S<sub>3</sub> for an output power of 500 W are shown in Fig. 7.

The selected parameters of the simulations are the same as the simulation 500 W prototype. These parameters are listed in Table IV. The maximum value of the current in these switches occurs at the negative state in simulation results as shown in Fig. 7. In the negative half-period of the grid, the circuit shifts between the negative and zero states. During the negative state, the capacitor  $C_1$  is charged by the capacitor C<sub>B</sub>, while the capacitor C<sub>2</sub> is discharged by the grid.

Fig:7 Simulations of the current of switches: (a) grid current ( $i_g$ ) [1 A/div], (b) ( $i_{s1}$ ) [2 A/div], (c) ( $i_{s3}$ ) [2 A/div].

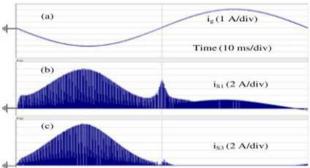

Therefore, the voltage difference between the capacitors C<sub>1</sub> and C<sub>B</sub> as well as the capacitors C<sub>1</sub> and C<sub>2</sub> is decreased. The equivalent circuits of the zero and negative states of the proposed topology for the current stress analysis are shown in Fig. 8(a) and (b), respectively. According to the electric arch and circuit theory, the grid voltage in series with a grid-side inductor (Lg) can be equivalent with the current source (ig) as shown in Fig. 8.

Fig.8. Equivalent circuit of the proposed converter during zero state and (b) negative state

According to Fig.8 (a), at the zero state

$$\frac{dv_{diff,1}}{dt} = \frac{v_{diff,1} - R_{ss}i_g}{(R_{e1} + R_{s3})C_{e1}}$$

(7)

$$\frac{dv_{diff,2}}{dt} = \frac{I_{pv}}{C_B} - \frac{v_{diff,1} - R_{s3}i_g}{(R_{c1} + R_{s3})C_1}$$

(8)

According to Fig.8 (b), at the zero state

$$\frac{dv_{diff,1}}{dt} = \frac{R_{Cb}I_{pv} + dv_{diff,2}}{(R_{cb} + R_{e\,2})C_1} + \frac{i_g}{C_2}$$

(9)

$$\frac{dV_{diff,2}}{dt} = \frac{I_{pv}}{C_B} + \frac{R_{cb}I_{PV} - V_{diff,1}}{R_{c2}C_{e2}}$$

(10)

Where in (8) -(11),  $R_{e2}$  and  $C_{e2}$  will be as follows:

$$R_{e2} = R_{D2} + R_{s1} + R_{C1} + R_{CB}, C_{e2} = \frac{C_1 C_B}{C_1 + C_B}$$

(11)

By using the averaging method at the switching cycle T<sub>s</sub>, and linearizing (8) – (11), the average value of  $i_{S1}$  and  $i_{S3}$  at the negative and zero states is equal to (13) and (14), respectively:

$$\frac{dv_{\text{diff},1}}{dt} = (1+s(t))\frac{v_{\text{diff},1} - R_{\text{S}}i_g}{(R_{\text{c}1} + R_{\text{c}2})C_{\text{c}1}} - s(t)(\frac{R_{\text{CB}}I_{PV} + v_{\text{diff},2}}{(R_{\text{CB}} + R_{\text{c}2})C_{\text{1}}} + i_gC_2)$$

$$\frac{dv_{\text{diff},2}}{dt} = (1+s(t))(\frac{I_{PV}}{C_B} - \frac{v_{\text{diff},1} - R_{\text{S}}i_g}{(R_{\text{c}1} + R_{\text{c}2})C_{\text{1}}}) - s(t)(\frac{I_{PV}}{C_B} + \frac{R_{\text{CB}}I_{PV} + v_{\text{diff},2}}{(R_{\text{c}2} + C_{\text{c}2})})$$

where s(t) denotes the switching state function given as

1 when the circuit is at positive state 0 when the circuit is at zero state -1 when the circuit is at negative state

The average current of  $_{iS1}$  and  $i_{S3}$  during  $T_s$  can be found as

$$\langle i_{s1} \rangle T_{2} = \frac{v_{diff,1} T_{s} = R_{s3} \langle i_{g} \rangle T_{s}}{R_{e1} + R_{s3}}$$

$$\langle i_{s1} \rangle T_{2} = \frac{v_{diff,2} T_{s} = R_{CB} I_{PV}}{R_{e2}}$$

(13)

$$\langle i_{s1} \rangle T_2 = \frac{v_{diff}, 2T_s = R_{CB}I_{PV}}{R_{e2}}$$

(14)

The simulation results of the current flowing through the switches S1 and S3 for the output power 500 W are shown in Fig. 7. The value of the current that passes through S1 and S3 to reach to its maximum at the negative state is shown in this figure too. At the negative state,

$$\langle i_{\text{sl, max}} \rangle T = \frac{1}{2} \left( \frac{C_1}{C_1 + C_2} + 1 \right) \left( \frac{M \operatorname{Im}}{1 - M} + \frac{T_s}{\operatorname{Re}_1 C_1} \frac{1 - M}{2} \right) \tag{15}$$

$$\langle i_{s3, \text{ max}} \rangle T = \frac{1}{2} \left( \frac{C_1}{C_1 + C_B} + 1 \right) \left( \frac{M \text{ Im}}{1 - M} + \frac{T_s}{\text{Re}_2 C_{e2}} \frac{1 - M}{2} \right)$$

(16)

Equations (22) and (23) indicate that the values of  $C_1/(C_1 +$  $C_2$ ) and  $C_1/(C_1 + C_B)$  should be calculated small enough, and the values of the Re1Ce1 and Re2Ce2 should be smaller than the switching period in order to minimize the current stress on the switches.

These values can be limited by a small resistor or a small inductor between the capacitors if needed. The relationship between the voltage and current passing through the capacitors is calculated by

$$i_c = C \frac{\Delta v_c}{\Delta t} \tag{17}$$

The required capacitance of C1 and CB for the proposed inverter can be derived by equalling the capacitor power magnitude to the grid power ripple magnitude. The capacitance C1 and CB can be calculated as follows:

$$C_1 \text{ or } B = \frac{I_{C_1} \text{ or } B(\max)}{\wedge (V_r V_n) f}$$

(18)

where  $I_{C1max}$  and  $I_{CBmax}$  are the maximum current that passes through the capacitors C<sub>1</sub> and C<sub>B</sub>, respectively. AVr, Vn, and f are the capacitor voltage ripple magnitude, nominal voltage on the capacitor, and the frequency during maximum current, respectively.

### 3.2. Conduction and Switching Losses of Power Devices During the positive power cycle, the grid current flows through switches S<sub>1</sub> and S<sub>2</sub> and the capacitor C<sub>1</sub> is charged through diode $D_2$ at the positive state as shown in Fig. 6(a)

and (g). The capacitor C<sub>1</sub> is charged through diode D<sub>2</sub> and switch  $S_1$  at the negative state as shown in Fig. 6(c) and (e). The voltage drop of the power devices can be derived by

MOSFET:

$$v_{DS}(t) = i(t)R_{DS}$$

(19)

Diode:

$$v_{AK}(t) = V_F + i(t) R_{AK}$$

(20)

where  $V_{DS}$  is the drain source voltage drop of the MOSFET, follows: R<sub>DS</sub> is the drain source resistance of the MOSFET during on the state operation, VAK is the anode cathode voltage drop of the diode, V<sub>F</sub> is the equivalent voltage drop under zero current condition of the diode, RAK is the anode cathode arch and resistance of the diode during the on state, and i(t) is the grid current. The average value of the conduction losses of the MOSFET switch (PMOSFET Cond) during half of the fundamental period is calculated by

$$P_{MOSFET\_Cond} = \frac{1}{\pi} \int_{0}^{\pi} v_{DS}(t) i(t) d_{MOSFET}(t) d\omega t \quad (21)$$

**Table I:** Duty Ratio of Each Conducting Device

| Semiconductor Devices | Duty ratio (d) Positive cycle (v <sub>g</sub> >0) Negative Cycle (v <sub>g</sub> <0) |                   |  |

|-----------------------|--------------------------------------------------------------------------------------|-------------------|--|

| $S_1$                 | $M \sin \omega t$                                                                    | M sin $\omega t$  |  |

| $S_2$                 | 1                                                                                    | $1-M\sin\omega t$ |  |

| $S_3$                 | $M \sin \omega t$                                                                    | $1-M\sin\omega t$ |  |

| $S_4$                 | 0                                                                                    | M sin $\omega t$  |  |

| $D_1$                 | 0                                                                                    | M sin $\omega t$  |  |

| $D_2$                 | $M \sin \omega t$                                                                    | 0                 |  |

The average value of the conduction loss in the diode (PDiode\_Cond) during the on state mode is calculated by

$$P_{Diode\_Cond} = \frac{1}{\pi} \int_{0}^{\pi} v_{AR} \dot{i}(t) d_{Diodes}(t) d\omega t$$

$$=\frac{1}{\pi}\int_{0}^{\pi}v_{F}i(t)R_{AK}i(t)dD_{lodes}(t)d\omega t \qquad (22)$$

The device manufacturer and circuit parameters for efficiency evaluation of proposed inverter are listed in Table II. The switching losses of the MOSFET switch can be found as follows:

Table II: Specifications and Power Devices for Efficiency Evaluation

| 2 / diddicion          |             |  |  |  |

|------------------------|-------------|--|--|--|

| Parameter              | Value       |  |  |  |

| Input Voltage          | 400 V       |  |  |  |

| Grid Voltage/Frequency | 220 V/50 Hz |  |  |  |

| Rated Power            | 500 W       |  |  |  |

| AC Output Current      | 2.3 A       |  |  |  |

| Switching Frequency    | 24 KHz      |  |  |  |

| Duty Ration (M)        | 0.78        |  |  |  |

$$P_{MOSFET}$$

$sw = f_{SW}E_{OSS}V_{F}$  (23)

where E<sub>oss</sub> is the stored energy that can be achieved from the datasheet that is equal to  $45 \mu J$ . The total switching losses of the switches in the proposed inverter can be derived as follows:

$$P_{Total \_sW} = 4 f_{SW} E_{OSS} V_F = 3.46W$$

(24)

### 3.3. Conduction Losses in the Capacitors

The ESR of the capacitors of the proposed inverter is achieved from aluminium electrolyte capacitor datasheets and it is divided into two parts. The second part of the conduction losses is related to the inrush current during the charging of the capacitors. These losses can be defined as

$$P_{CAP\_Cond} = \frac{2(R_{C1} + R_{CB})}{\pi} \int_{0}^{\pi} d_c(t) i_{s1}^2(t) d\omega t \quad (25)$$

$$P_{CAP\_Cond\_2} = \frac{2(R_{C1} + R_{C2})}{\pi} \int_{0}^{\pi} d_c(t) i_{s3}^2(t) d\omega t \quad (26)$$

where dc(t) is the duty ratio of the capacitor.

## 3.4. Control Scheme

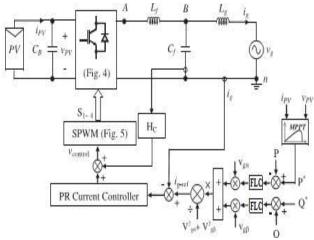

The control strategy of the proposed grid-tied single-phase inverter is shown in Fig. 9. It contains two cascaded loops [21]: the first loop is an inner control loop, which has the responsibilities to generate a sinusoidal current and the outer control loop is implemented for the current reference generation, where the power is controlled. The transfer function of this controller can be found as follows:

Fig.9. Control block diagram of the proposed single-phase grid-tie inverter based on single-phase PQ theory

$$G_{PR(s)} = K_p + \frac{2K_r}{s^2 + \omega^2}$$

(27)

where  $k_{\text{p}}$  is the proportional gain,  $k_{\text{r}}$  is the fundamental resonant gain, and  $\omega$  is the resonant frequency. According to the single-phase PQ theory the current reference can be produced by regulating the active and reactive powers. The active power (P) and reactive power (Q) for the proposed topology can be calculated by

$$P = \frac{v_{ga}i_{ga} + v_{g}\beta i_{g}\beta}{2}, \ Q = \frac{v_{ga}i_{ga} - v_{g}\beta i_{g}\beta}{2}$$

(28)

where  $v_{g\alpha}$  ,  $v_{g\beta}$  ,  $i_{g\alpha}$  and  $i_{g\beta}$  are the  $\alpha$  and  $\beta$  components of grid voltage and current, respectively. The active power and reactive power references (P\* and Q\*) can be tuned by the operators  $\{R-3\}$  or in the control unit, when the MPPT control is activated. If PI controllers are used for power regulations,

the grid current reference (ig-ref) can be derived as follows

$$i_{g-ref} = \frac{1}{v_{ga-v^2g\beta}^2} [v_{ga}v_{g\beta}] {Gp(s) \quad (P-P^*) \atop Gq(s) \quad (Q-Q^*)}$$

(29)

where  $G_p(s)$  and  $G_q(s)$  are the PI controllers for active power and reactive power, respectively. The LCL filter is adopted as the grid interfaced filter in this proposed topology. High output current quality in the proposed inverter can be obtained if the output filter is configured correctly. The inverter-side inductor (L<sub>f</sub>) value is calculated by considering 10–20% of the ripple on the output current, which is given and

$$L_f = \frac{(v_{dc} - v_{An})(M \sin \omega t)}{f_{SW} \Delta i_L}$$

(30)

where  $f_{sw}$  is the switching frequency and  $\Delta i_L$  represents the peak-to-peak ripple current on the Lf. The inverter output volt age  $(v_{An})$  can be calculated as follows:

$$v_{An} = MV_{dc} \sin \omega t \tag{31}$$

By replacing (39) with (38) and simplifying it, we have

$$L_f = \frac{(v_{dc})(RF)}{f_{SW}\Delta i_L} \tag{32}$$

where RF is the ripple current and can be calculated from

$$RF = M \sin \omega t - M^2 \sin^2 \omega t \tag{33}$$

The maximum achievable value of modulation index (M) is  $RF_{max}$  = 0.25 [26]. The maximum value of the filter capacitor is calculated by (42), limiting to be less than 5% of the nominal value [27]

$$C_{F, \text{ max}} = \frac{0.05 P_n}{2\pi f V_{\text{max}}^2}$$

(34)

where  $P_n$  is the nominal power,  $V_{rms}$  denotes the root mean square (RMS) grid voltage, and f presents the grid frequency. There is a relation between the inverter-side inductor (L<sub>f</sub>) and the grid side (Lg). This value is determined with the ratio between the ripple attenuation (r) as described in [28]

$$L_g=rL_f (35)$$

### 4. Fuzzy Logic Controller

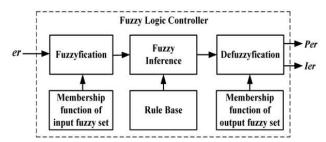

In FLC, basic control action is determined by a set of linguistic rules. These rules are determined by the system. Since the numerical variables are converted into linguistic variables, mathematical modelling of the system is not required in FC.

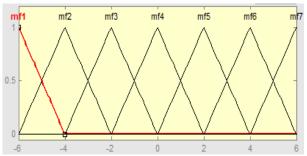

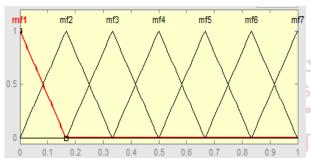

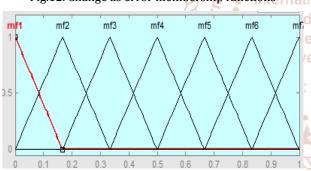

The FLC comprises of three parts: Fuzzification, interference engine and Defuzzification. The FC is characterized as

- Seven fuzzy sets for each input and output.

- Triangular membership functions for simplicity.

Fig. 10. Fuzzy logic controller

- Fuzzification using continuous universe of discourse.

- Implication using Mamdani's 'min' operator.

- 5. Defuzzification using the height method.

**Table III:** Fuzzy Rules

|    | NB | NM | NS | ZE | PS | PM | PB |

|----|----|----|----|----|----|----|----|

| NB | NB | NB | NB | NB | NM | NS | ZE |

| NM | NB | NB | NB | NM | NS | ZE | P5 |

| NS | NB | NB | NM | NS | ZE | PS | PM |

| ZE | NB | NM | NS | ZE | PS | PM | PB |

| PS | NM | NS | ZE | PS | PM | PB | PB |

| PM | NS | ZE | PS | PM | PB | PB | PB |

| PB | ZE | PS | PM | PB | PB | PB | PB |

Fuzzification: Membership function values are assigned to the linguistic variables, using seven fuzzy subsets: NB (Negative Big), NM (Negative Medium), NS (Negative Small), ZE (Zero), PS (Positive Small), PM (Positive Medium), and PB (Positive Big). The input error for the FLC is given as

$$E(k) = \frac{P_{ph(k)} - P_{ph(k-1)}}{V_{ph(k)} - V_{ph(k-1)}}$$

(36)

$$CE(k) = E(k) - E(k-1)$$

(37)

- **Inference Method:** Several composition methods such as Max-Min and Max-Dot have been proposed in the literature. In this paper Min method is used. The output membership function of each rule is given by the minimum operator and maximum operator. Table 1 shows rule base of the FLC.

- **Defuzzification:** As a plant usually requires a non-fuzzy value of control, a Defuzzification stage is needed. To compute the output of the FLC, "height" method is used and the FLC output modifies the control output. Further, the output of FLC controls the switch in the inverter.

To achieve this, the membership functions of FC are:

- 1. Error

- 2. Change in error

- 3. Output

The set of FC rules are derived from

$$u = -\left[\alpha E = (1 - \alpha) * C\right] \tag{38}$$

Fig.11. input error as membership functions

Fig.12. Change as error membership functions

Fig.13. Output variable membership functions

Where  $\alpha$  is self-adjustable factor which can regulate the whole operation. E is the error of the system; C is control variable.

### 5. Simulation Results

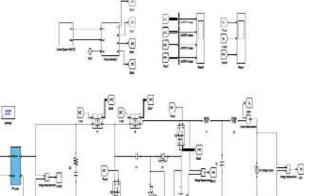

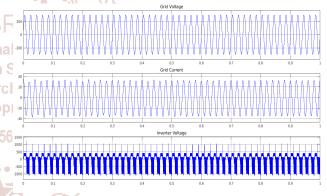

In fig 14 the proposed grid connected inverter has been presented. The simulation results of the proposed gridconnected inverter operation are presented in Fig 15.

Table IV Parameters for the 500 W Prototype

| Parameter                            | Value                       | Parameter                   | Value         |  |

|--------------------------------------|-----------------------------|-----------------------------|---------------|--|

| Power rating (P)                     | 500 W                       | Capacitance $(C_1)$         | 220 μF, 500 V |  |

| Input voltage (Vdc)                  | 400V                        | Capacitance $(C_2)$         | 330 μF, 500 V |  |

| Output voltage<br>(v <sub>Bn</sub> ) | 220 V (RMS)                 | $L$ filter ( $L_f$ )        | 4 mH          |  |

| Input capacitor $(C_B)$              | 470 $\mu$ F, 500 V          | C filter $(C_f)$            | $2.2 \mu F$   |  |

| Power switches $(S_1 - S_4)$         | C2M0080120D, SiC<br>MOSFET  | $L_g$                       | 2 mH          |  |

| Diodes $(D_1, D_2)$                  | C3D10060A<br>Schottky Diode | Switching frequency $(f_s)$ | 24 kHz        |  |

Fig.14. simulation block diagram of proposed single-phase transformer less grid-connected inverter

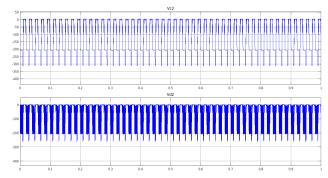

From Fig. 15, it is clear that the output current and voltage of the proposed inverter are highly sinusoidal with low harmonic distortion due to the three-level inherency of the output voltage. The current harmonic distribution is demonstrated in Fig. 10.

Fig. 15 Simulation results of the proposed topology (a) Grid Voltage (b) Grid Current (c) Inverter Voltage

It is clear that the pulse duration of the output voltage (v<sub>An</sub>) is in agreement with the switching frequency. The voltage stress of the capacitors and diodes is shown in Fig. 16.

Fig. 16 Simulation results of the capacitor and diode voltages (a) Capacitor Voltage (b) Diode Voltage

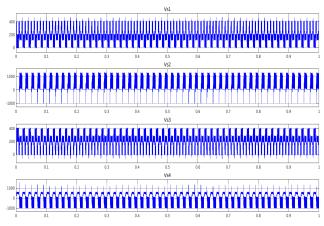

Simulation results for drain source voltage of switches are shown in Fig. 17

Fig. 17 Simulation results of the Switches (a)  $V_{s1}$  (b)  $V_{s2}$  (c)  $V_{s3}$  (d) $V_{s4}$

### 6. Conclusion

In this paper we are implementing a new single-phase transformer less inverter for a grid-tied PV system using a charge pump circuit concept with the fuzzy controller. Therefore, the main concept of the proposed system is to generate the negative output voltages which have been developed in this proposed inverter. Here we are using the fuzzy logic controller for the better performance because the fuzzy controller is the most suitable for the human decisionmaking mechanism, providing the operation of an electronic system with decisions of experts. Therefore, we are developing the proposed topology which is similar to the neutral line in the grid; therefore, the leakage current will be suppressed and the transformer is eliminated. Moreover, the proposed topologies have the capability to deliver the in Science required reactive power into the grid. Therefore, the arch an photovoltaic inverter topology for efficiency proposed topology is used to realize the minimum number of components and higher power density can be achieved with lower design cost. By using the simulation result we can verify the proposed system.

#### References

- [1] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid connected inverters for photovoltaic modules," IEEE Trans. Ind. Electron., vol. 41, no. 5, pp. 1292-1306, Sep./Oct. 2005.

- [2] X. Guo, R. He, J. Jian, Z. Lu, X. Sun, and J. M. Guerrero, "Leakage current elimination of four-leg inverter for transformer less three-phase PV systems," IEEE Trans. Power Electron., vol. 31, no. 3, pp. 1841-1846, Mar. 2016.

- [3] T. Bruckner, S. Bernet, and H. Guldner, "The active NPC converter and "its loss-balancing control," IEEE Trans. Ind. Electron., vol. 52, no. 3, pp. 855–868, Jun. 2005.

- [4] Swapna Popat God, Anil Tekale, Mallareddy C., "Control Scheme based on Quasi Z-Source Network for Four Switch Three Phase Brushless DC Motor", in IJSRD, vol.5, issue 07, ISSN-2321-0613, page. No. 461-462, June 2017.

- [5] D. Barater, E. Lorenzani, C. Concari, G. Franceschini, and G. Buticchi, "Recent advances in single-phase transformer less photovoltaic inverters," IET Renewable Power Generation, vol. 10, no. 2, pp. 260–273, 2016.

- [6] B. Yang, W. Li, Y. Gu, W. Cui, and X. He, "Improved transformer less inverter with common-mode leakage current elimination for a photovoltaic grid connected power system," IEEE Trans. Power Electron., vol. 27, no. 2, pp. 752-762, Feb. 2012.

- [7] F. Bradaschia, M. C. Cavalcanti, P. E. P. Ferraz, F. A. S. Neves, E. C. Santos, and J. H. G. M. da Silva, "Modulation for three-phase transformer less z-source inverter to reduce leakage currents in photovoltaic systems," IEEE Trans. Ind. Electron., vol. 58, no. 12, pp. 5385-5395, Dec. 2011.

- [8] Y. Gu, W. Li, Y. Zhao, B. Yang, C. Li, and X. He, "Transformer less inverter with virtual dc bus concept for cost-effective grid-connected PV power systems," IEEE Trans. Power Electron., vol. 28, no. 2, pp. 793– 805, Feb. 2013.

- W.-J. Cha, K.-T. Kim, Y.-W. Cho, S.-H. Lee, and B.-H. Kwon, "Evaluation and analysis of transformer less improvement and reduction of leakage current," IET Power Electron., vol. 8, no. 2, pp. 255-267, 2015.

- 45[10] TH. Xiao and S. Xie, "Leakage current analytical model and application in single-phase transformer less photovoltaic grid-connected inverter," IEEE Trans. Electromagnetic Compat., vol. 52, no. 4, pp. 902-913, Nov. 2010.

- [11] W. Yu et al., "High-efficiency inverter with H6-type configuration for photovoltaic non-isolated ac module applications," in Proceeding. Annual. IEEE Appl. Power Electron. Conf. Expo., 2010, pp. 1056-1061.

- Tekale Anil A, Ghule Puja R., "Switched DC Sources [12] Based Novel Multilevel Inverter", in IRJET, vol.4, issue.6, 2017, ISSN- 2395-0056, pp. 123-127.